Install and Run

What Are the System Requirements?

We recommend having at least 8GB of memory and about 1GB of free disk space available for Sigasi Visual HDL (SVH).

Does SVH Run on My OS?

Windows and Linux

You can check out the system requirements for your version of SVH on the Release Notes page.

Diagrams

To use the diagrams on Linux, you require a GLIBC version >=2.17 and the following libraries

- libX11.so.6

- libstdc++.so.6

- libpthread.so.0

- libc.so.6

- libdl.so.2

- libgobject-2.0.so.0

- libglib-2.0.so.0

- libnss3.so

- libnssutil3.so

- libsmime3.so

- libnspr4.so

- libatk-1.0.so.0

- libatk-bridge-2.0.so.0

- libcups.so.2

- libdrm.so.2

- libgio-2.0.so.0

- libm.so.6

- libXcomposite.so.1

- libXdamage.so.1

- libXext.so.6

- libXfixes.so.3

- libXrandr.so.2

- libgbm.so.1

- libexpat.so.1

- libxcb.so.1

- libxkbcommon.so.0

- libdbus-1.so.3

- libasound.so.2

- libatspi.so.0

- libgcc_s.so.1

- ld-linux-x86-64.so.2

- libffi.so.6

- libpcre.so.3

- libplc4.so

- libplds4.so

- librt.so.1

- libgssapi_krb5.so.2

- libgnutls.so.26

- libavahi-common.so.3

- libavahi-client.so.3

- libz.so.1

- libgmodule-2.0.so.0

- libselinux.so.1

- libresolv.so.2

- libXrender.so.1

MacOS

SVH is not supported on MacOS. See here.

How Do I Verify My Sigasi Download?

The SHA1 sum (or hash) is a fingerprint of a file. After you download a file, you can check if it was downloaded correctly by calculating its SHA sum and comparing it to ours. If the SHA sum is the same, you can be sure that the download was successful: no one touched it while downloading (man-in-the-middle), nor did your antivirus corrupt the file.

We have SHA1 sums available for our .vsix files here .

Linux

On Linux, you can compare the .vsix you downloaded to our SHA1 sum using the command sha1sum -c vs-code-sha1.txt. Note that the the SHA1 sum .txt file should be next to your .vsix file. For example,

$ ls

sigasi-visual-hdl-linux.vsix vs-code-sha1.txt

$ sha1sum -c vs-code-sha1.txt --ignore-missing

sigasi-visual-hdl-linux.vsix: OK

Windows

On Windows, you can compute the SHA using MD5 & SHA Checksum Utility .

What Are the License Server Requirements?

The license server (FlexNet) is supported on

- Red Hat Enterprise Linux 5.2 (32-bit and 64-bit) or newer

- Windows 7 (32-bit and 64-bit) or newer

The instructions to set up the license server can be found here.

How Can I Update Sigasi?

See the manual.

What If I Want to Get Back to My Old Toolflow? Am I locked In?

If you ever want to get back to your old tools (we hope you won’t), you’ll have absolutely no trouble doing so. All your files are just the way you left them, except that we created two hidden files in your project folder (.project and .library_mapping.xml). You can leave them sitting there or you can delete them after you stop using our tool.

In short: you are not locked in at all!

How Does Sigasi Change My Existing Project?

You do not have to change your directory structure, the names of your VHDL files or anything in your project folder. The only thing SVH does is add a few hidden files with project information.

Can I Use Features From an Upcoming Release?

Yes! You can find the details at Sigasi Visual HDL Preview (2026.1).

Licensing

One License Structure

If you purchase an SVH license, you can use this for either VS Code, Eclipse, or both. If you have floating licenses, each running instance of Sigasi will check out one floating license. Please note that Sigasi will be ramping down our development for Eclipse over the coming year.

Do You Sell Floating Licenses?

Absolutely. Our Sales Team will be happy to set you up with floating licenses, which are based on the well-known FlexNet (a.k.a. FlexLM) license manager.

What Are the Requirements for the License Server?

License server requirements are listed at the license server system requirements.

My New License Contains a Start Date in the Future. When Can I Start Using It?

If you’re renewing your license, the new license file can contain a start date in the future. As long as the start date is part of the VENDOR_STRING, it will not be enforced and you can start using your new license file immediately.

Getting Started

Which Sigasi Files Should I Add to My Revision Control System?

Sigasi stores all project information in two files (.project and .library_mapping.xml) and one directory (.settings). If you track these files, you have everything you need.

.projectdescribes all generic information on your project: which files belong to your project, etc..library_mapping.xmldescribes the mapping of your VHDL libraries..settings(if it exists) is a directory that contains additional settings

You can revert to older revisions of these files while Sigasi is running. Sigasi will update as soon as the files are refreshed.

Editing

What Do You Mean By “Type-Time”?

“At type-time” means “while you type.” The Sigasi development environment checks your code at type-time. In other tools, your code gets checked only after you save all files and explicitly start a compiler, but Sigasi has a type-time compiler. While you are typing, the Sigasi compiler checks your code and marks your errors.

Related terms include:

- Save-time: the moment you you save your file

- Elaboration-time: the moment you you set the top level of your design

- Simulation-time (or run-time): during the simulation

Does Sigasi Support Multi-Byte Characters?

Yes, Sigasi supports all unicode characters, including Japanese. Note that the VHDL language does not allow any non-ASCII characters as identifiers, so you cannot use multi-byte characters in signal names.

Configure

How Can I Make Sigasi Generate Spaces Instead of TABs?

See the manual entry on Indentation and Whitespace.

Where Is Path Variable Information Stored?

Path variable information is stored in the .project file.

You can find more info here.

Warnings and linting rules

Can Sigasi Replace My Linter?

Depending on which features you use, it could.

But Sigasi’s linter does not aim to replace your $100,000 power lint checker with CDC (clock domain crossing) checks. Instead, Sigasi’s linter helps you get the coding conventions right first time around. In addition to style linting, Sigasi’s linter can interface with your third-party power linter tool (like Aldec ALINT), giving you feedback faster. Contact us to discuss your requirements.

How Fast Is the Sigasi linter?

Depending on your exact coding rules, the Sigasi linter can flag violations either within seconds after you type (type-time linting) or after you save (save-time linting). We can check over 80% of common coding rules at type time.

How Can I Organize My Errors and Warnings (Problem Markers) in the Problems View?

See the manual entries on Problems View for VS Code and Problems View for Eclipse.

Does SVH’s Built-In Linter Replace My Code Reviews?

No.

The Sigasi linting functionality is aimed at freeing up time wasted in code review meetings, time wasted on trivial things like naming conventions and deprecated data types. We hope you can use this time to discuss complex design decisions and computation algorithms that have an impact on the product you are designing.

What Kind of Linting Rules Are Possible?

The answer to this question is not straightforward. However, some examples may help. We can implement (but are not limited to) the following types of custom linting rules:

- Naming conventions (e.g. constants should be in capitals, signals should start with “s”, etc.)

- Deprecated libraries, data types, constructs (e.g. don’t use block statements; don’t use

std_logic_unsigned, etc.) - Project structure, file names (e.g. an entity should be in a file named “_e.vhd”)

- Required file headers

- Maximum sizes of files, processes, etc.

- How to instantiate components/entities

- Unused signals, constants, etc.

- Dead code

- and much more…

We cannot implement overly complex or fuzzy requirements like:

- Post-synthesis checks

- CDC checks

- Fuzzy requirements like: “Entities should be sufficiently commented.” (How can an algorithm decide what is sufficient?)

If you get in touch with us, we will evaluate your coding rules to determine which rules we can implement.

I Typed an Error in my VHDL Code. Why Didn’t Sigasi Catch It?

SVH does not attempt to check the full correctness of your VHDL and Verilog code. We just run a set of syntax and “general sanity” checks. This way, 90% of common errors are caught before you even start your simulator.

As you design, you put your code through a funnel: Sigasi finds the first 90% of errors in your code, without ever running a simulation. Next, you compile with the simulator and you find another bunch of problems. In each successive step of your design flow, you find harder-to-track errors in your design. Sigasi helps you get a big number of issues out of the way early on, so that you can concentrate on finding the hard problems down the road.

Features

Does SVH Support VHDL-2008?

SVH supports VHDL-2008 features. Inline PSL is not supported, but PSL in comments is safely ignored.

Why Don’t You Have Feature XYZ? How Can I Put It on Your Roadmap?

As any tech company, our stack of good ideas is far larger than the amount of time we have to work on them. We’re grateful for any suggestions that users send us and we often build new features based on these. However, we have to prioritize and maybe your favorite feature is not on our short-term roadmap.

Deciding which features to put on the roadmap is a very complicated process. Some of the things that help are:

- If your feature is useful for all users, not just your specific case.

- If your feature brings a lot of value to you and to other users. For example, a feature that saves you thirty seconds each month brings less value than something that saves you half a day each week.

Feel free to talk to us about any feature, big or small.

How Do I Create a Component Declaration (“Paste As” in Emacs)?

Some other editors (most notably Reto Zimmermann’s Emacs VHDL Mode) have the concept of “port translation”. You first copy the source code of an entity declaration, and then you can paste it as an instantiation or as a component declaration.

Sigasi supports the same, but in a different way: we use Autocomplete. You don’t need to go find the original entity declaration, since Sigasi knows where to find it in your project.

For more information, see the manual entries on Autocompletion in VS Code and see Autocompletion in Eclipse.

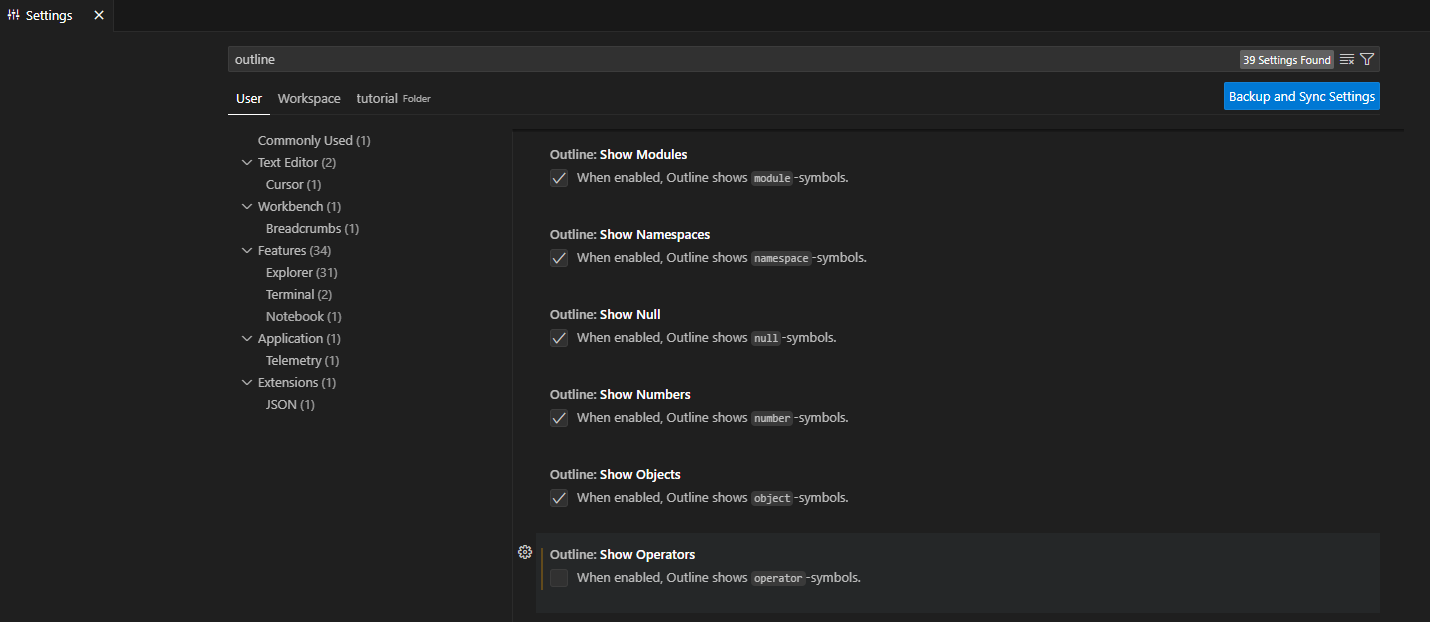

How Do I Hide Signal Assignments in Outline?

VS Code offers an array of settings to hide symbols from the outline. If you specifically want to hide signal assignments, you have to disable outline.showOperators in the VS Code settings. To do this, navigate to File > Preferences > Settings (or use the shortcut Ctrl+,), and then search for outline.showOperators.

Troubleshooting

How Can I Check Whether SVH Started Successfully?

To check whether SVH started successfully, you should navigate to Sigasi’s output view. You can do this by opening the Command Palette (Ctrl+Shift+P) and selecting Sigasi: Open Log.

The Output View should say Language client connected from ...

The logs in the Sigasi output view might contain errors from the client and server. If errors are present, please copy them and include them in your email to support+vscode@sigasi.com.

OutOfMemoryError: Java Heap Space

If Java runs out of memory, you will see java.lang.OutOfMemoryError: Java heap space in the log.

To avoid this, go to the settings (Ctrl+Shift+P > Preferences: Open Settings (UI) > Sigasi) and set the Sigasi > Server: Arguments. Increase the value for Xmx to more than the default 8g.

Sigasi Switches My Keyboard Layout! Did I Find a Bug?

This sometimes happens on Windows. You probably triggered a keyboard shortcut that switches your keyboard layout. Read Microsoft’s documentation on Language bar keyboard shortcuts . If you only use your local keyboard layout and not a standard English layout, you might as well disable the language bar.

I Get Lots of Errors in Files that Are Not Really Part of My Project. Can I Hide Them?

Legacy projects tend to accumulate files that are no longer strictly necessary. These files are still on your disk, or even in your revision control system, but the scripts don’t feed them to the simulator or to the synthesis tools any more.

We recommend removing these junk files that accumulate over time. If you are using a revision control system, you can always go back, so there is no risk to removing stale files. However, if there is a good reason to keep junk files in the project folder, you can excluded them from all libraries by right-clicking the files and selecting Remove from build.

What Is a MAC Address and How Do I Find Mine?

Sigasi node-locked licenses are locked to the unique MAC address (NIC address) of your computer’s network interface. An example of a MAC address is: 00:1c:42:00:00:09.

A computer can have a long list of MAC addresses, both from physical and virtual network adapters. We recommend using a MAC address belonging to a physical network adapter since some types of virtual network adapters tend to change their MAC addresses occasionally.

You can find out which interface a MAC address belongs to depending on your OS.

- Windows: in a command prompt, type

ipconfig /allto get a detailed list of interfaces. On Windows 10 you need to avoid choosing the WiFi adapter MAC address when the random hardware addresses privacy feature is enabled . Your Sigasi license will become invalid once the WiFi MAC address changes. - Linux: in a terminal type

/sbin/ip addrorifconfigto obtain a detailed list. The interface for wired ethernet is usuallyeth0. - Mac OS: go to System Preferences… > Network then select the desired physical interface and select Advanced… > Hardware.

Alternatively you can type

ifconfigin a terminal.

Floating licenses also require a MAC address, but this needs to be the MAC address of the license server. Ask your system administrator.

How Can I Solve LD_LIBRARY_PATH or LD_PRELOAD Issues?

Note that certain environment variables like LD_LIBRARY_PATH and LD_PRELOAD in your environment may break SVH.

The initialization scripts of some third-party tools set these variables to incompatible values.

When this is detected by SVH, the log file contains The LD_LIBRARY_PATH has been set to: ... Note that this may cause side-effects.

If SVH fails to open the editor, state machine and block diagrams, or the documentation view, check that these variables are either undefined or empty. If they are not, try to start VS Code from the command line as follows:

LD_LIBRARY_PATH="" LD_PRELOAD="" code

Where Can I Find the Log Files?

On some occasions, we might ask you to share (tracing) logs. SVH’s client and server debug logs can be viewed in the Sigasi Output View. SVH’s tracing logs contain the communication between client and server and can be seen in the Sigasi Tracing Output View. You can open it using the Sigasi: Open Tracing Log. As detailed below, the log severity can be configured and they’re also saved to files.

Before obtaining server logs, it’s best to enable debug logging.

For more detailed logging, open the settings and change Sigasi > Server > Log: Level to debug.

Also set Sigasi > Trace: Server to verbose.

The location of the server logs depends on your OS.

- On Linux, the logs are below

~/.config/Code/logs - On Windows, the logs are in

%AppData%\Code\logs

Then find [datetime]/window[1]/exthost/output_logging_[datetime]/[0-9]-Sigasi{Tracing}.log.

For each occurrence of [datetime], choose the most recent directory available. Please send us both the debug log and the tracing log.

We recommend opening the exthost folder using the command Developer: Open Extension Logs Folder.

Note: These logs contain file names from your project, so only send them to us if you’re allowed to do so.

If you want to enable fine grained logging to help us debug a very specific problem, check out the Fine grained logging How To.

Why Is Sigasi Trying to Get Through My Firewall?

There are a number of reasons why Sigasi connects to the internet.

- Updates: Each time you start Sigasi, the program checks to see if there are new updates from our website (currently located at

https://download.sigasi.com). Sigasi downloads the updates in the background and, when done, it asks you if it can install them. - Talkback

Enhanced Security: Customers with strict security policies can contact us to discuss compliance with their policies.

I Have Error Markers in Files that Are Not Mapped to a Library. What’s This?

Sometimes, unmapped files have error markers. This can happen if a compilation did not complete normally. You can select these errors from the Problems View and remove them by pressing delete. If you rebuild the project, no new error markers will be generated for the VHDL files that are not mapped to a library.

How Can I Undo “Exclude from Build”?

If you accidentally excluded a file from the VHDL or Verilog build, you can easily undo this by right-clicking the file again and selecting Change Library. Next, select the library in which this file needs to compiled.

If you use a version control system, you can also revert the .library_mapping.xml file. SVH will automatically pick up changes to this file and update the library information.

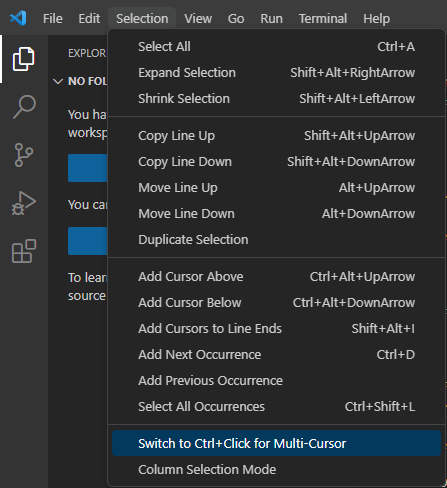

Why Doesn’t Ctrl+Click Work?

If Ctrl+Click doesn’t Open Declaration, it’s likely caused by an incorrect VS Code setting. In the VS Code Selection menu, there is an entry to switch the multi-cursor modifier to Ctrl+Click.

Even accidentally clicking that entry (e.g., when trying to enable Column Selection Mode) will change the setting for the multi-cursor modifier. This results in Alt+Click being used when trying to Open Declaration instead of the usual Ctrl+Click. You can click that same entry again to switch back to using Ctrl+Click.

Other tools

Which Free VHDL Simulator Can I Use?

Sigasi does not offer simulators. If you don’t have a VHDL simulator yet, we would recommend the following simulators. You can download them free of charge.

| Simulator | Comment | Download from | Windows | Linux | MacOS |

|---|---|---|---|---|---|

| Aldec Lattice Edition | Only Lattice FPGAs | Lattice Download page | Yes | No | No |

| Aldec Active-HDL, Student Edition | Students only | Aldec Download page | Yes | No | No |

| ModelSim-Intel FPGA Edition | Only Intel FPGAs | Intel Quartus Web Edition | Yes | Yes | No |

| ISim | Only AMD/Xilinx FPGAs | Xilinx Webpack | Yes | Yes | No |

| GHDL | open-source | GHDL download page | Yes | Yes | Yes |

We’ve not had good results with FreeHDL or with Green Mountain VHDL. It seems that these two projects may have been terminated.