The first release of Sigasi® Visual HDL™ (SVH™) for 2025 features various UX improvements, a new VHDL linting rule and improved VHDL highlighting, and many small fixes.

TL;DR

SVH 2025.1 adds many UX improvements and gives some extra love to VHDL.

We are expanding the set of Code Lenses. They allow to open the State Machines Diagram, add unmapped files to the project, export documentation, and one to export the compilation order. Additionally, Code Lenses can now individually be enabled and disabled.

We are also introducing a variant of Code Lenses, Inlay Hints. These fulfill the same action as Code Lenses—providing extra contextual actions or information—but they are displayed inline rather than on a line above the code.

Exploring your design or testbench top-down has never been as easy. The new Top Level Pickers allow you to easily list and select the correct top level design unit or root UVM component.

For VHDL, we have added a new linting rule to detect superfluous resets, complementing our existing reset analysis.

New semantic tokens make the highlighting of your code much more detailed. These are fully customizable, allowing you to make your theme truly yours.

We have also made it easier to see information about the license used for Sigasi CLI through a separate --license option.

As a cherry on top, this release includes over 50 bug fixes and miscellaneous improvements.

Actually, there is one more thing… We are working on a new onboarding experience, making it easier to include really complex projects. Are you interested in simplifying your complex project setup? Get in contact with our Support Team.

Code Lens

Code Lenses provide access to key features right from your editor. You can find them above the most important elements in your code. We added a new Code Lens above processes and always blocks to open the State Machines Diagram. Additionally, at the top of unmapped files, you will find a Code Lens to add the file to the project.

While much can be achieved through Code Lenses, having many of them enabled—especially when using many extensions—can make your editor look cluttered.

For this reason, Sigasi’s Code Lenses can now be individually enabled and disabled through the sigasi.editor.codeLens.* settings. All of them are enabled by default, except for the following two new Code Lenses:

- Export documentation; above modules, entities, architectures, and configurations

- Export the Compilation Order; above modules, entities, architectures, and configurations

These lenses allow you to perform these export tasks quickly, with the corresponding design unit as the top level.

Inlay Hints

This release introduces a new feature: Inlay Hints. These are similar to Code Lenses, they can add additional actions or show additional information about the code. However, Code Lenses are shown on a line above the code, whereas these hints are displayed inline at the end of code lines that contain state machine transitions. It is shown as an arrow (➚) and Ctrl+Clicking it makes you navigate to the relevant state in the editor.

Top Level Pickers

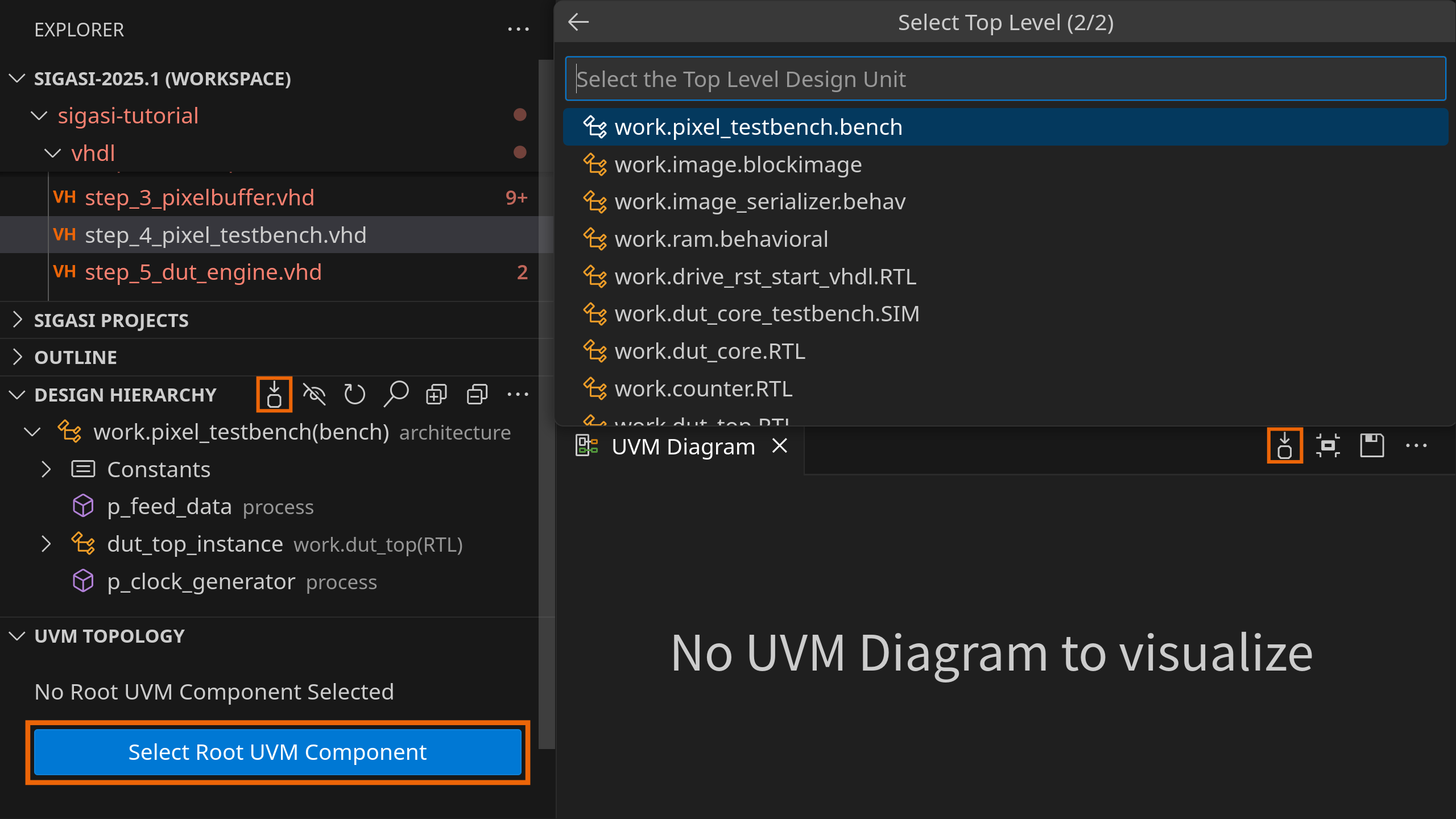

Getting an overview of all top level design unit or root UVM component candidates is difficult. That is where our new Top Level Pickers come in. These buttons on the toolbars of the Design Hierarchy View, UVM Topology View, and UVM Diagram allow you to easily list all valid top levels and root UVM components and select the correct one. If none was set yet, the buttons are emphasized in the view.

Learn more: Design Hierarchy View

Learn more: UVM Topology View

Learn more: UVM Diagram

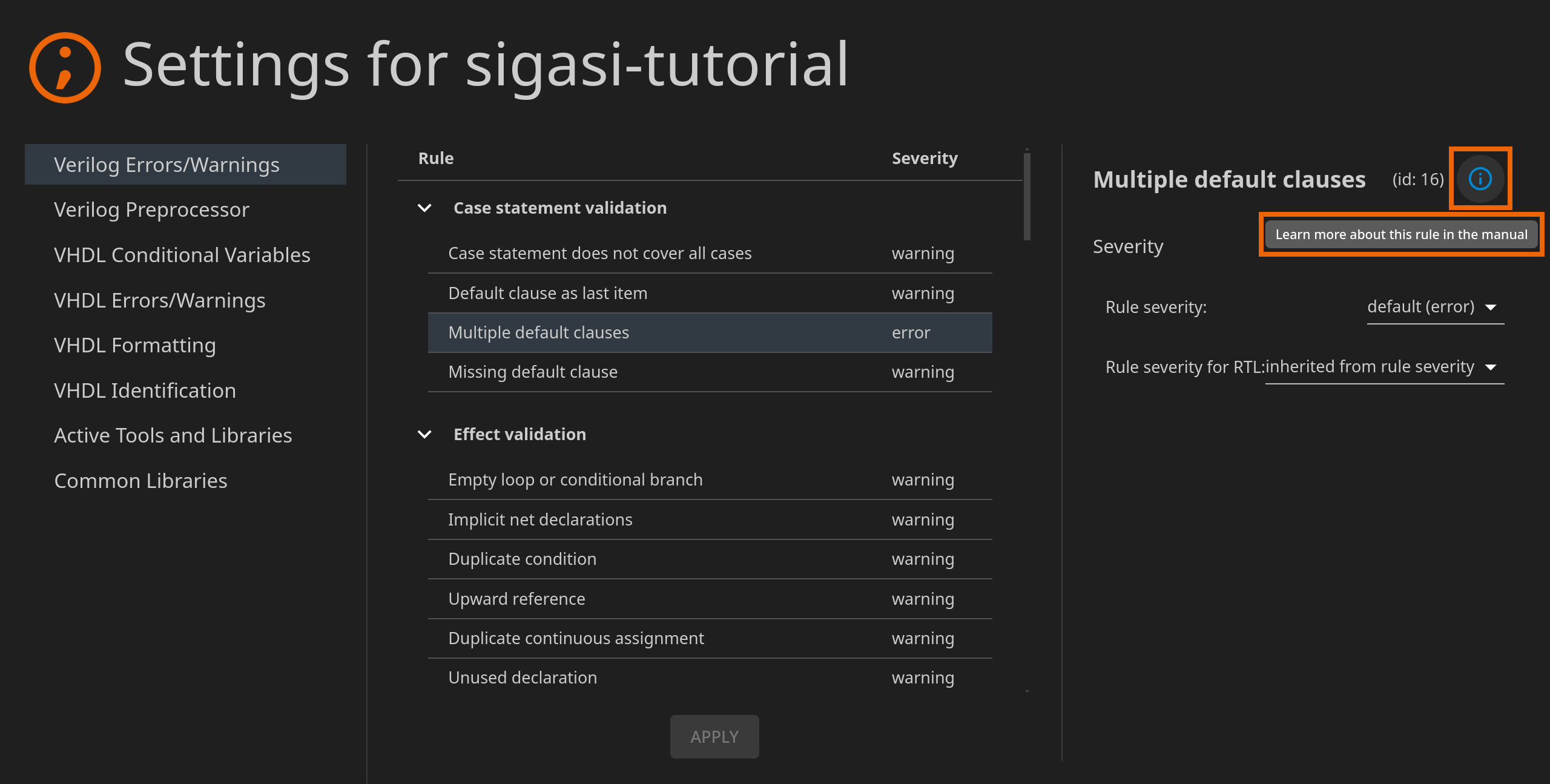

Linting Rule Manual Links

Understanding and configuring linting rules is not easy. Usually, it helps to read a short explanation or look at an example. In the settings page, all linting rules now have a link to our manual, so you can learn all about the rules and their configuration.

VHDL

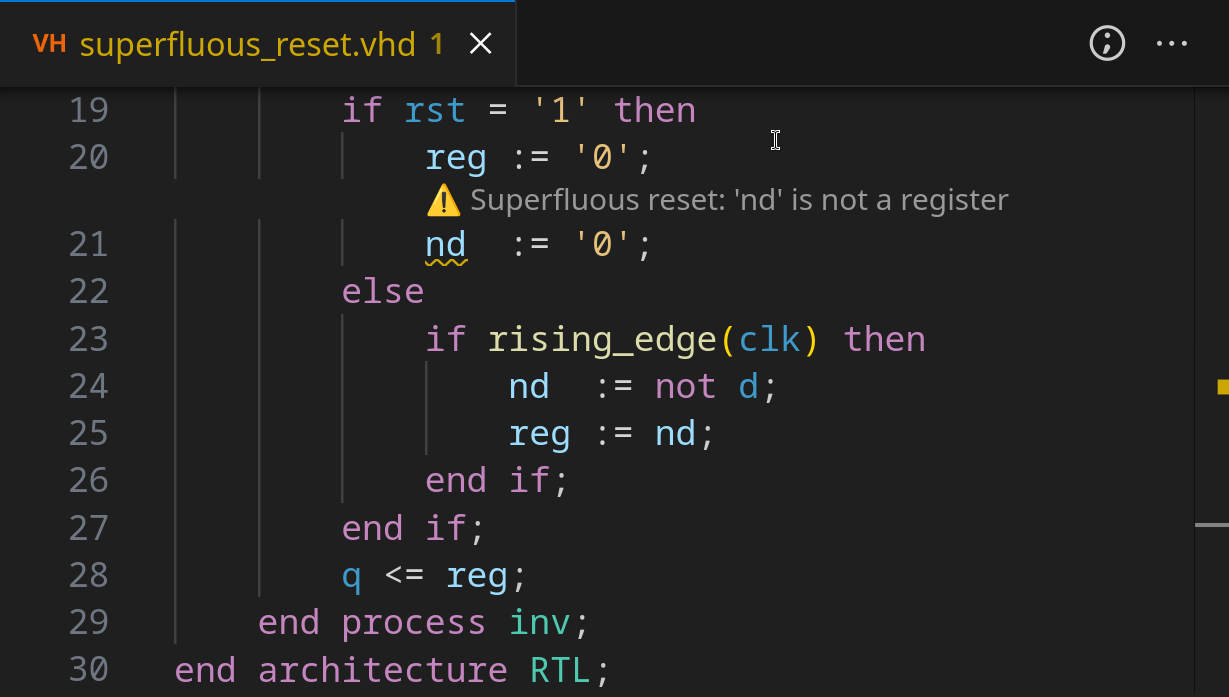

New Linting Rule

Superfluous Reset

Complementing the Incomplete reset branch linting rule, SVH 2025.1 introduces a rule that marks superfluous resets. For example, combinational logic preceding clocked processes does not require a reset.

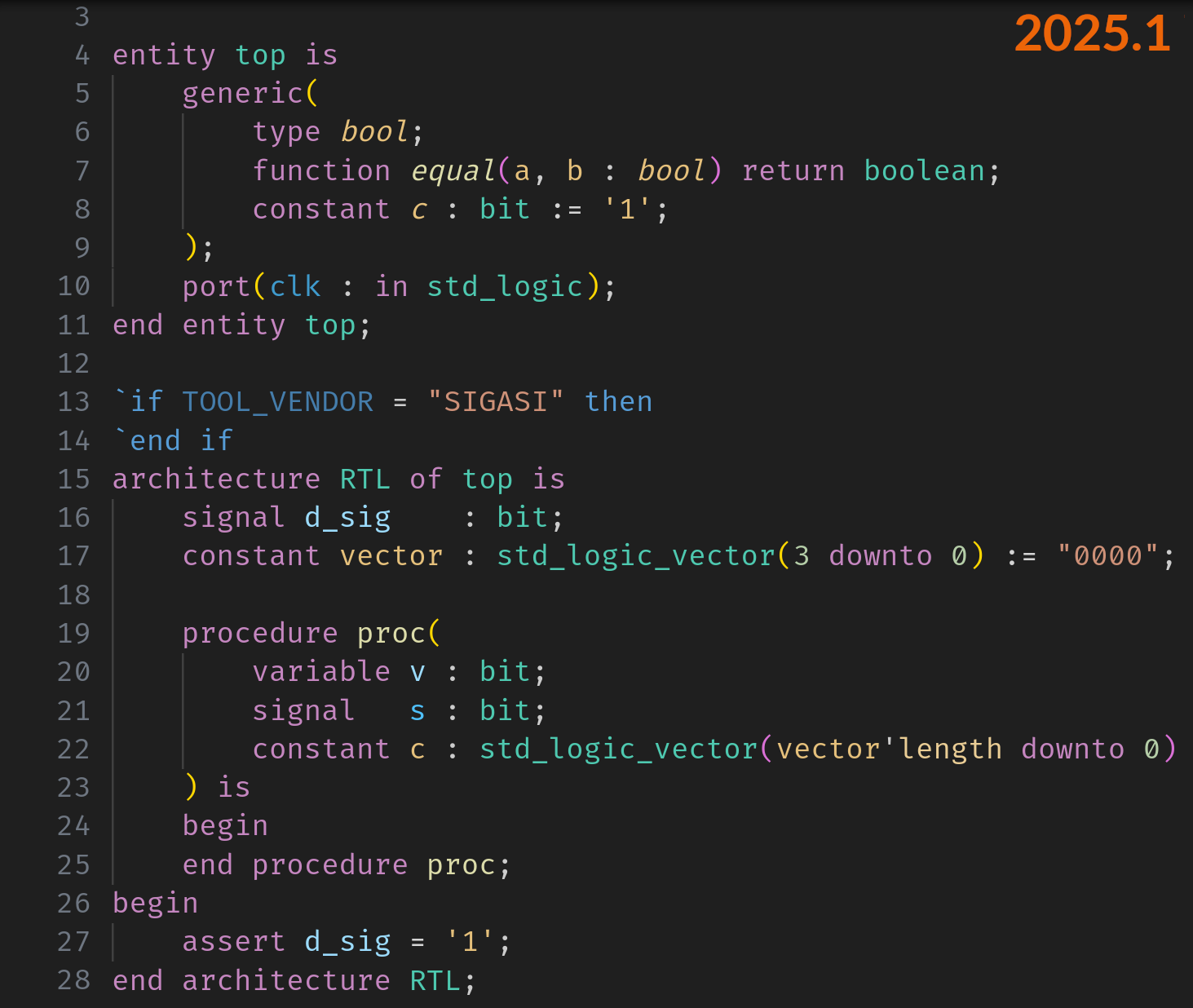

Learn moreSemantic Highlighting Improvements

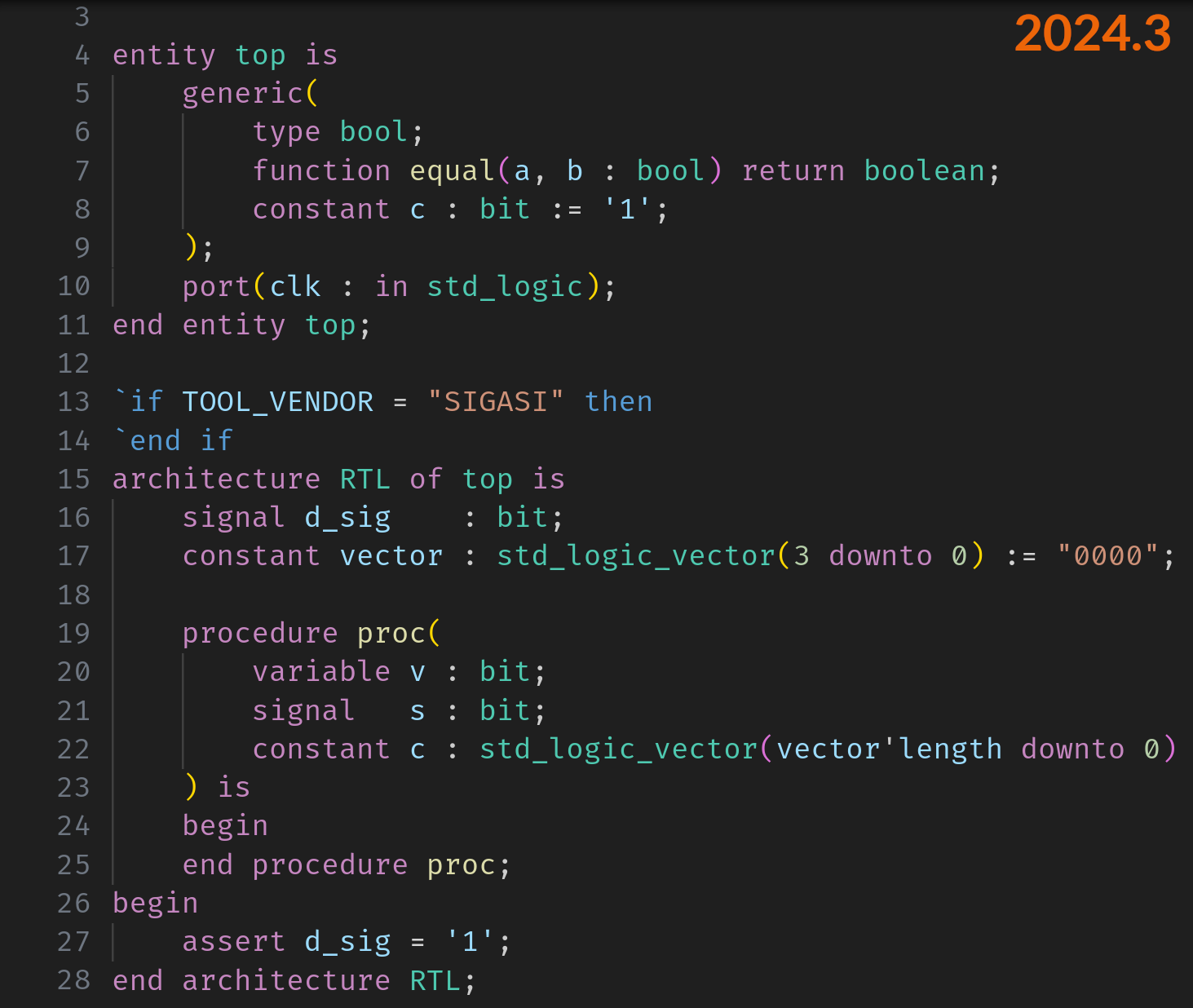

We differentiated many constructs by coloring them differently. For example, signals, constants, and variables are now visually distinguishable. You can fully customize these colors through the following new semantic tokens using the

- Port

- Conditional processing variable

- Signal

- Subprogram variable parameter

- Subprogram signal parameter

- Subprogram constant parameter

- Constant

- Attribute

- Generic constant

- Generic type

- Generic subprogram

Sigasi CLI

We added a --license option to the Sigasi CLI to inspect the used license. It can also be used to debug why your license is not working as expected. We made the --version much faster and removed the need to acquire a license to use this option.

Additionally, a message was added when no issues are found using the verify command.

Quality of Life

- Clarified icons for enabled and disabled state in the Class Hierarchy View

- Added a warning when renaming to an illegal identifier, e.g., renaming to a keyword

- Added

Workspace SettingsandUser Settingsto theConfigurecontext menu in the Sigasi Projects View - Automatically select the project in the Export Documentation and Export Compilation Order dialog if there is only one project

- Verilog Added function and struct field signatures in autocomplete suggestions

- Verilog Added constructor and inheritance hints and class item qualifiers to members in the Class Hierarchy View

- VHDL Added autocomplete templates for

recordandenumwhen typing those keywords as prefixes

Further New and Noteworthy

- Bump the Language Server’s maximum memory usage to 12 GB if your machine has 32 GB or more available

- Added a button in the memory status bar item to run the JVM Garbage Collector and a corresponding command

- Added a checkbox to disable and enable specific autocomplete templates in the Templates Editor

- Simplified library configuration quick pick

- Improved wording in documentation generation dialog

- Improved wording in the Documentation View

- Restyled the

Revert to Defaultbutton in the Templates Editor - Removed the unused

Auto Insertproperty in the Templates Editor - Improved the tutorial

- Improved the error feedback of the

Add tool or librarydialog - Verilog Improved contrast of Prohibited macros in settings page

- Verilog Prevented adding the same include path twice

- Verilog Disabled navigation for double-clicks on the collapse & expand icon in the UVM Diagram

- Verilog Removed the collapse & expand icon in the UVM Diagram if there are no children

- Verilog Prevent setting the library of

.hand.vhfiles as their library depends on their include context - Verilog Improved linking for implicit declarations in

covergroups - VHDL Removed the

Add signalQuick Fix in packages as signals are rarely wanted in this context - VHDL Improved finite state machine computation

Bug Fixes

- Fixed typo in the memory status bar item

- Fixed typos regarding state machines

- Fixed

Extracting JREmessage - Fixed server failing to start when an empty server argument is configured

- Fixed hover text color on Community Edition pages

- Fixed settings page input field repositioning when an error message is shown

- Fixed selection when switching pages in the Templates Editor

- Fixed the layout of the

Add tool or librarydialog on small screens - Fixed missing refreshes when links to linked resources in the

.projectare broken - Fixed missing valid keyword autocompletion suggestions

- Added a warning when project dependencies are used in the

.projectas those are not supported - Removed duplicate

Export documentationcommand - Fixed cursor for libraries in the Dependencies Diagram

- Verilog Fixed opening the Class Hierarchy View when a file is present multiple times in your project

- Verilog Fixed false positive linking error when changing the library mapping of include files

- VHDL Fixed false positive Unexpected keyword capitalization error on attributes

- VHDL Fixed false positive

No matching subprogramerror with'subtypeand'baseattributes - VHDL Fixed false positive Positional Association in Instantiations error for subprograms with a single argument

- VHDL Fixed false positive

Invalid function parameter modeandInvalid variable parameter in functionerrors in VHDL 2019 when usinginoutvariables - VHDL Fixed rare missing

A positional assocation cannot follow after a named associationerror - VHDL Allowed keywords as VHDL 2019 conditional processing identifiers

Updates

- Updated our minimum supported VS Code version to 1.80 from 1.77

- Renamed

PreferencestoSettings- Renamed the

Configure > Open Project Preferencescontext menu item toConfigure > Project Settings - Renamed the

Sigasi: Open Preferencescommand toSigasi: Open Settings

- Renamed the

- Renamed the

Set as UVM Topology TopCode Lens toSet as Root UVM Component - Removed the editor context menu items to set Design Top Levels and Root UVM Components in favor of Top Level Pickers

Sigasi Visual HDL 2025.1.1 Point Release

On April 1, we released Sigasi Visual HDL 2025.1.1. This release contains the following changes and bug fixes:

- Improved the UI for RTL Severity in the VHDL and Verilog Errors/Warnings settings pages

- Fix compilation order export for specified top levels

- Verilog Fixed invalid include paths on Windows

- Verilog Updated Verible to

v0.0-3820-g3415c94d - Verilog Added a new configurable SystemVerilog-specific style linting rule:

Non-blocking assignments should not be used in functions. It checks the same issue as the Non-blocking assignments are not allowed in functions for Verilog. However, in SystemVerilog this is allowed, but discouraged.

Sigasi Visual HDL 2025.1.2 Point Release

On April 18, we released Sigasi Visual HDL 2025.1.2. This release contains the following changes and bug fixes:

- Verilog Added support for

//pragma protect begin_protectedand//pragma protect end_protected - Verilog Added support for

`protectand`endprotect - VHDL Fixed false positive Missing label warning on subprogram prototype declarations

Sigasi Visual HDL 2025.1.3 Point Release

On May 30, we released Sigasi Visual HDL 2025.1.3. This release contains the following changes and bug fixes:

- VHDL Fixed false positive error when using composite records containing constrained 2D arrays of unconstrained records

- Verilog Added support for referring to cross coverage from other cross coverage

- Verilog Treat

.svafiles as SystemVerilog by default

Update or Install

If you have downloaded SVH from the VS Code Marketplace , your installation will automatically update.

You can also download the latest .vsix file and manually install it in VS Code.

- Linux: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-linux.vsix

- Windows: https://download.sigasi.com/vs-code/updates/latest/sigasi-visual-hdl-win32.vsix

The SHA sum is downloadable from https://download.sigasi.com/vs-code/updates/latest/vs-code-sha1.txt .

System Requirements

Sigasi Visual HDL requires:

- Windows 10 or Windows 11 64-bit

- Red Hat Enterprise Linux RHEL 8 or 9 64-bit

- VS Code >= 1.80 and < 2.0

We recommend having at least 8 GB of memory and about 1 GB of free disk space available for Sigasi Visual HDL.

Feedback

Our Support Team happily welcomes any of your feedback.

Transition Information

You can transition to VS Code right away with your existing projects and licenses, but if you want a little more time, we have you covered with Sigasi Visual HDL in Eclipse.

We will start ramping down support for Eclipse in 2025. Please check these release notes for information specific to using SVH in Eclipse and whom to talk to about your transition.