Tired of hunting for HDL answers?

If you were using Sigasi Visual HDL, you’d already have them. Try our free Community Edition today—and experience the smarter way to work with HDL.VHDL provides several ways to assign values to a signal based on the value of another.

Most of the time, there’s more than one valid approach, and each has its advantages

depending on clarity, maintainability, and tool support. This guide covers three primary

idioms: selected signal assignment (with/select), conditional signal assignment

(when/else), and case statements inside processes.

VHDL-2008 introduced a 4th idiom: pattern matching in case statements.

We’ll conclude with practical considerations for using the right construct.

1. Selected Signal Assignment (with / select)

The with/select construct assigns a value to a signal based on the exact value of a selector. It’s compact and avoids redundancy by evaluating the selector only once.

with a select b <=

"1000" when "00",

"0100" when "01",

"0010" when "10",

"0001" when "11",

"0000" when others;

Pros:

- Concise and readable for simple mappings.

- Avoids repeated conditions.

Cons:

- Only supports equality checks.

- Cannot handle more complex logical conditions.

VHDL Tip: Ensure that all possible values are covered, especially with enumerated types. Use a when others clause to handle unspecified cases, both for robustness and synthesis compatibility. Newer VHDL revisions (2008 and 2019) reinforce this best practice and allow slightly broader use of expressions in the selector, such as concatenation.

2. Conditional Signal Assignment (when / else)

This form allows each value assignment to be guarded by a Boolean expression, enabling more flexibility than with/select.

b <= "1000" when a = "00" else

"0100" when a = "01" else

"0010" when a = "10" else

"0001" when a = "11" else

"0000";

Pros:

- Supports complex or non-mutually-exclusive conditions.

- More expressive than with/select.

Cons:

- Conditions can become verbose with long signal names.

- Each condition must repeat the comparison explicitly.

Note: Although VHDL-2019 introduced conditional (ternary-like) expressions to simplify such assignments, not all tools support this yet, so it’s best used selectively.

3. Combinational Process with case Statement

The most general approach uses a process block and a case statement, allowing more complex behavior and procedural control.

process(all)

begin

case a is

when "00" => b <= "1000";

when "01" => b <= "0100";

when "10" => b <= "0010";

when "11" => b <= "0001";

when others => b <= "0000";

end case;

end process;

Pros:

- Most flexible and readable for complex logic.

- Allows additional control like reporting, assertions, or logging.

Cons:

- Slightly more verbose due to boilerplate (process and sensitivity list).

Best Practice:

Use process(all) to avoid missing signals in the sensitivity list, which can lead to

simulation mismatches. This syntax became standardized in VHDL-2008 and widely

adopted since.

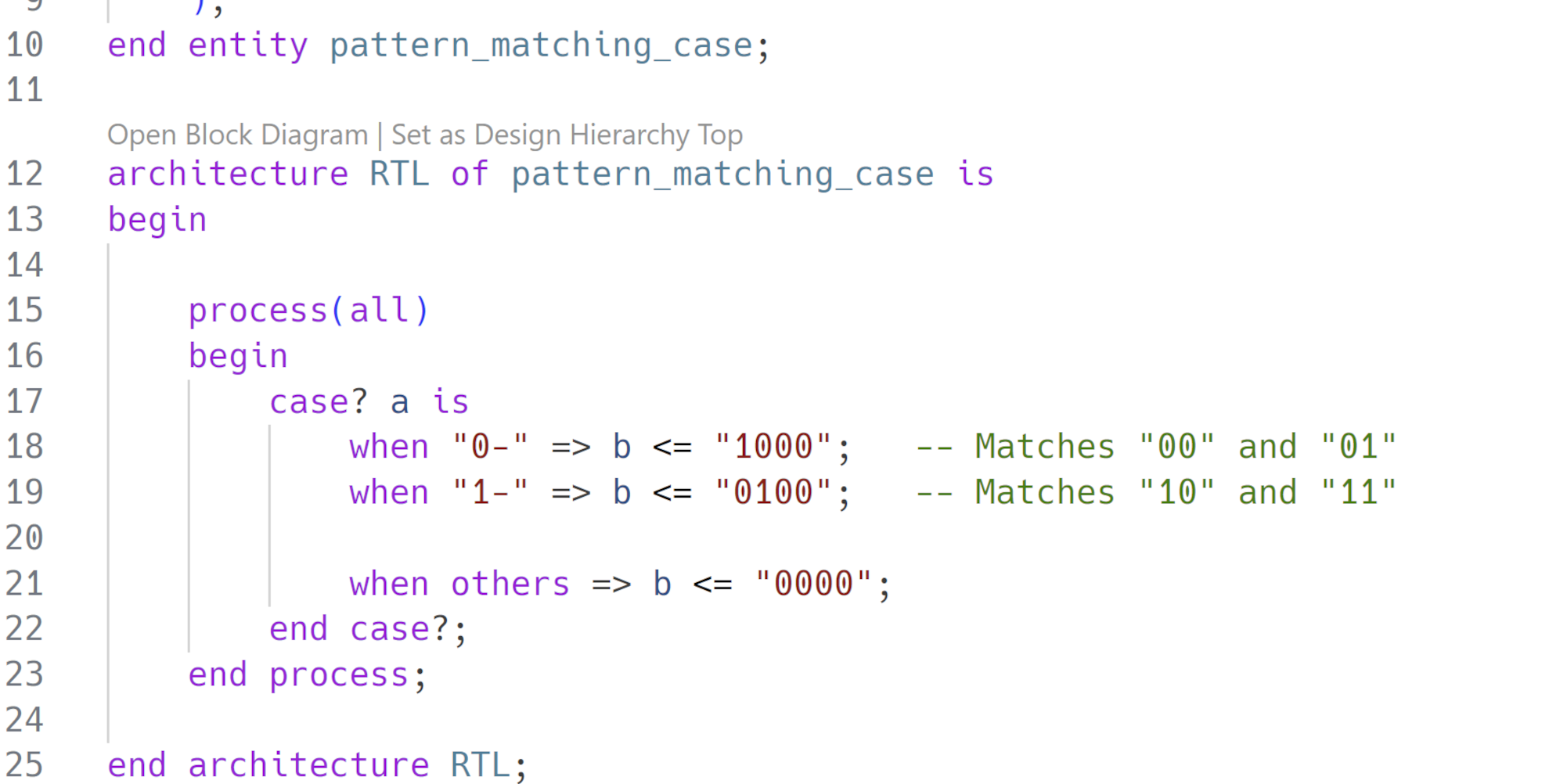

4. Pattern Matching in Case Statements

VHDL-2008 introduced pattern matching (case?) with don’t-care symbols (-), useful for

grouping input patterns.

process(all)

begin

case? a is

when "0-" => b <= "1000"; -- Matches "00" and "01"

when "1-" => b <= "0100"; -- Matches "10" and "11"

when others => b <= "0000";

end case?;

end process;

This method is particularly handy for compacting logic and allowing synthesis tools to optimize hardware by leveraging don’t-care conditions.

Choosing the Right Construct

Each style suits different situations:

| Method | Best For |

|---|---|

| with/select | Simple one-to-one mappings |

| when/else | Complex Boolean conditions |

| case in process | Flexibility, control, and structured logic |

| case? | Grouping patterns with don’t-care bits |

Practical Considerations

- Consistency: Teams often standardize on one or two idioms across a project.

- Tool Support: Not all synthesis tools fully support the latest language features—check tool documentation if using VHDL-2019-specific syntax.

- Robustness: Always include default cases (when others) to avoid simulation or synthesis surprises.

Tip: Many designers keep a concise reference like the Doulos Golden Reference Guide close at hand to recall subtle syntax differences. Whether using classic styles or experimenting with modern features, choose what keeps your code clear, correct, and maintainable.

Ready to stop searching and start designing?

Sigasi Visual HDL helps you focus on what matters—writing better HDL, faster. Discover the difference with our free Community Edition.See also

- Records in VHDL: Initialization and Constraining unconstrained fields (blog post)

- Finite State Machine (FSM) encoding in VHDL: binary, one-hot, and others (blog post)

- "Use" and "Library" in VHDL (blog post)

- VHDL Pragmas (blog post)

- Verification is eating the schedule (news)